Chapter 10

## **Memory & Simple I/O Interfacing**

### **Expected Outcomes**

Explain the importance of tri-state devices in microprocessor system

- Distinguish basic type of semiconductor memory and their applications

- Relate the address and data bus for various memories

- Describe I/O interfacing concept such as I/O driver and memory mapped

Relate the role of latch and buffer in interfacing with simple I/O devices

## **Tri-state Devices**

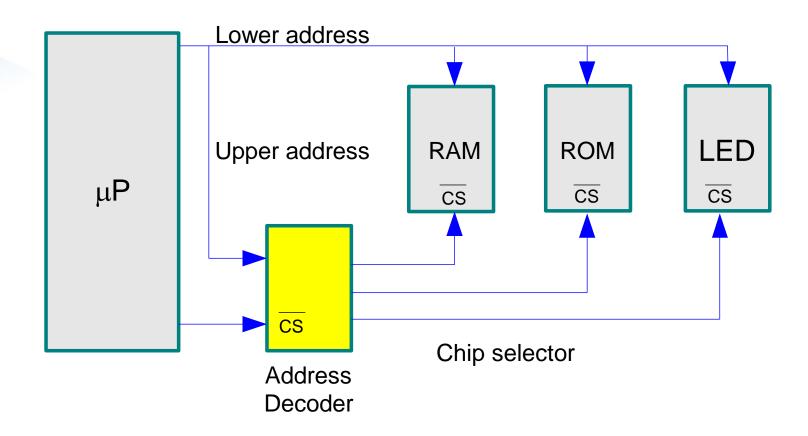

Any devices connected to a microprocessor should configure in tristate

- This is because only one device can communicate with the processor at one time leaving other devices at high impedance

- Devices with tristate outputs have an enable input such as OE, CS, E, etc

- With this configuration, there will not be any devices fighting for control of common wire which may cause damaging to current flow

Common devices connected to µP

Address decoder

Memory (ROM/RAM)

Input devices such as keyboard, mouse, switch etc

Output devices such as printer, monitor, LED, LCD

## **Tri-state Devices**

## Memory

## Memory

### Memory system is used to store data and instruction

## Type of memory

## ROM (Read Only Memory)

- Nonvolatile data remains even the power is off

- Normally used to store vectors, self-test routine, monitor program, common subroutine and etc

- Special device is required to store program in ROM

## RAM (Random Access Memory)

- Volatile type as data are lost as the power is off

- Temporary storage and normally used for operation and application system

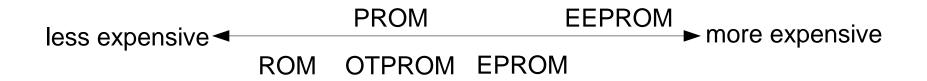

## ROM

### Programmable Maskable ROM

- Very cheap and normally is programmed in factory for mass production

- One-time written and widely used in game cassette

### Programmable ROM (PROM)

- One-time written and can be programmed by using PROM programmer

- One-time PROM (OTPROM)

- Cheap version of PROM with plastic packed

### Flash Memory

ROM

Like EEPROM, but erasing process involves block-by-block

Common in digital camera & MP3

## EPROM

### Common industrial EPROM

Common industrial EEPROM

2816

2864

- 2 kbyte (2048 x 8 bits) 4 kbyte (4096 x 8 bits) 8 kbyte (8192 x 8 bits) 16 kbytes (16384 x 8 bits)

- 32 kbytes (32768 x 8 bits)

2 kbyte (2048 x 8 bits)

8 kbyte (8192 x 8 bits)

| Part No   | Capacity | Org    | Access | Pins | Vpp        |

|-----------|----------|--------|--------|------|------------|

| 2716      | 16K      | 2Kx8   | 450ns  | 24   | 25V        |

| 2732      | 32K      | 4Kx8   | 450ns  | 24   | 25V        |

| 27C32-1   | 32K      | 4Kx8   | 450ns  | 24   | 25V CMOS   |

| 2764-20   | 64K      | 8Kx8   | 200ns  | 28   | 21V        |

| 27C64-12  | 64K      | 8Kx8   | 120ns  | 28   | 12.5V CMOS |

| 27128-25  | 128K     | 16Kx8  | 250ns  | 28   | 21V        |

| 27C256-15 | 256K     | 32Kx8  | 150ns  | 28   | 12.5V CMOS |

| 27C512-15 | 512K     | 6Kx8   | 150ns  | 28   | 12.5V CMOS |

| 27C010-15 | 1024K    | 128Kx8 | 150ns  | 32   | 12.5V CMOS |

| 27C020-15 | 2048K    | 256Kx8 | 150ns  | 32   | 12.5V CMOS |

| 27C040-15 | 4096K    | 512Kx8 | 150ns  | 32   | 12.5V CMOS |

## **EEPROM & Flash Chip**

### Some common EEPROM

| Part No   | Capacity | Org   | Speed | Pins | Vpp     |

|-----------|----------|-------|-------|------|---------|

| 2816A-25  | 16K      | 2Kx8  | 250ns | 24   | 5V      |

| 2864A     | 64K      | 8Kx8  | 250ns | 28   | 5V      |

| 28C64A-25 | 64K      | 8Kx8  | 250ns | 28   | 5V CMOS |

| 28C256-15 | 256K     | 32Kx8 | 150ns | 28   | 5V      |

### Some common Flash Chips

| Part No   | Capacity | Org    | Speed | Pins | Vpp      |

|-----------|----------|--------|-------|------|----------|

| 28F256-20 | 256K     | 32Kx8  | 200ns | 32   | 12V CMOS |

| 28F010-15 | 1024K    | 128Kx8 | 150ns | 32   | 12V CMOS |

| 28F020-15 | 2048K    | 256Kx8 | 150ns | 32   | 12V CMOS |

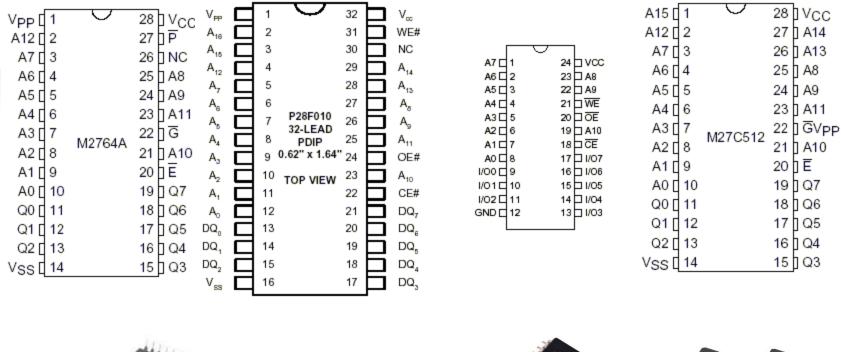

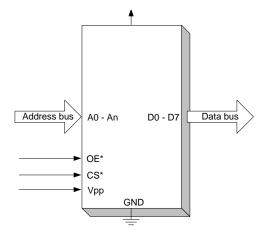

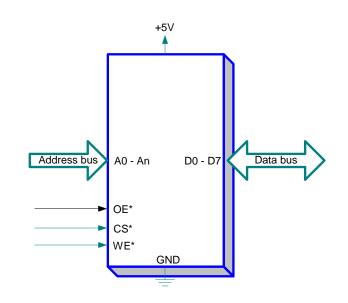

## **EPROM Pin Function**

### A0-An (Address Bus)

Address bus directly connected to lower address of microprocessor

### DO-Dn (Data Bus)

Data bus directly connected to data bus

## CS\* (Chip Select)

To activate EPROM and connected to address decoder

# OE\* (Output Enable) ROM place data into data bus

## **EPROM Pin Function**

### Vpp

Used by EPROM programmer to change bit in the chipPlace into high when it is not used

| CS* | OE* | Functions                                                         |

|-----|-----|-------------------------------------------------------------------|

| 1   | 0   | IC disable with minimum power consumption                         |

| 1   | 1   | IC disable with minimum power consumption                         |

| 0   | 0   | Read mode; data are placed on data bus                            |

| 0   | 1   | Wait state mode; data are placed on the bus when OE* is activated |

# **EPROM Memory Chip**

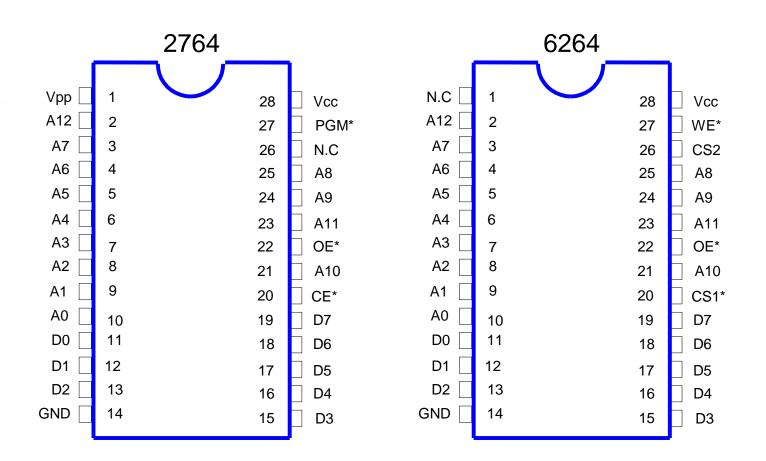

### Examples of Parallel EPROMs

|                                                                         | 2716                                                                  | 2732                                                                  | 2764                                                                                | 27128                                                                               | 27256                                                                               | 27512                                                                               |                                                                                  | 2716                                                                     | 2732                                                                     | 2764                                                                                   | 27128                                                                                  | 27256                                                                                  | 27512                                                                                      |

|-------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14 | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | Vpp<br>A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | Vpp<br>A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | Vpp<br>A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | A15<br>A12<br>A7<br>A6<br>A5<br>A4<br>A3<br>A2<br>A1<br>A0<br>D0<br>D1<br>D2<br>GND | 28<br>27<br>26<br>25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15 | Vcc<br>A8<br>A9<br>A11<br>OE*<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 | Vcc<br>A8<br>A9<br>A11<br>OE*<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 | Vcc<br>PGM<br>N.C<br>A8<br>A9<br>A11<br>OE*<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 | Vcc<br>PGM<br>A13<br>A8<br>A9<br>A11<br>OE*<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 | Vcc<br>A14<br>A13<br>A8<br>A9<br>A11<br>OE*<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 | Vcc<br>A14<br>A13<br>A8<br>A9<br>A11<br>OE*/Vpp<br>A10<br>CE<br>D7<br>D6<br>D5<br>D4<br>D3 |

## RAM

## Two basic types of RAM

### Static RAM (SRAM)

Easy to be used and requires an internal flip-flop to store each bit

Need 4 – 6 transistor for each FF and suitable for small system

4 times compact than SRAM with the same size

Normally used in personal computer

### Dynamic RAM (DRAM)

- Cheaper as dynamic RAM uses a single transistor that acts like a charged capacitor to store each bit

- Since the charge leaks, a DRAM must use refresh circuit to recharge the capacitor periodically (typically every 2 ms)

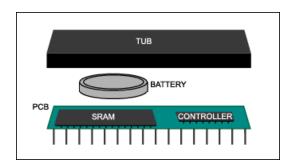

# RAM & NVRAM

### Performance difference

- DRAM contain more data per chip size

- SRAM is faster and simpler

- NV-RAM (Non-volatile RAM) is introduced to allow the CPU to read and write to it and not lost the content even the power is turned off

- To retain the content, the NVRAM chip internally

- Uses extremely power efficient CMOS

- Uses an internal lithium battery as backup energy

- ■Uses intelligent control circuitry to monitor Vcc pin and activates internal power if needed

- Thus the NV-RAM is expensive because it must provide the facilities in a single IC

## **SRAM & DRAM**

### Examples of SRAM & DRAM

| Part No    | Capacity | Org   | Speed | Pins | Vpp            |

|------------|----------|-------|-------|------|----------------|

| 6116P-1    | 16K      | 2Kx8  | 100ns | 24   | CMOS           |

| 6116LP-3   | 16K      | 2Kx8  | 150ns | 24   | CMOS           |

| 6264P-10   | 64K      | 2Kx8  | 100ns | 28   | CMOS           |

| 62256LP-10 | 256K     | 32Kx8 | 100ns | 28   | Low Power CMOS |

| 62256LP-12 | 256K     | 32Kx8 | 120ns | 28   | Low Power CMOS |

| Part No   | Capacity | Org    | Speed | Pins |

|-----------|----------|--------|-------|------|

| 4164-15   | 64K      | 64Kx1  | 150ns | 16   |

| 41256-15  | 256K     | 256Kx1 | 150ns | 16   |

| 511000P-8 | 1M       | 1Mx1   | 80ns  | 18   |

### NV-RAM from Dallas Semiconductor

| Part No      | Capacity | Org   | Speed | Pins |

|--------------|----------|-------|-------|------|

| DS1220Y-150  | 16K      | 2Kx8  | 150ns | 26   |

| DS1225AB-150 | 64K      | 8Kx8  | 150ns | 28   |

| DS1230Y-85   | 256K     | 32Kx8 | 85ns  | 28   |

## RAM

# Common industrial RAM 6116 2 kbyte (2048 x 8 bits) 6164/6264 8 kbyte (8192 x 8 bits) 43256/6625 32 kbytes (32768 x 8 bits)

A0-An (Address Bus) - Address bus directly connected to lower address of microprocessor

**DO-Dn (Data Bus) -** Data bus directly connected to data bus

CS\* (Chip Select) - To activate EPROM and connected to address decoder

**OE**\* (Output Enable) - RAM places data into data bus

**WE\* (Write Enable) -** RAM stores data into cell

### ■ The role of CS\*, OE\* and WE\*

RAM

| CS* | OE* | WE* | Functions                                |  |  |  |  |

|-----|-----|-----|------------------------------------------|--|--|--|--|

| 1   | Х   | Х   | C disable with minimum power consumption |  |  |  |  |

| 0   | 0   | 0   | Undefined                                |  |  |  |  |

| 0   | 0   | 1   | Read mode; data are placed on data bus   |  |  |  |  |

| 0   | 1   | 0   | Write mode; data are latched             |  |  |  |  |

| 0   | 1   | 1   | Wait state mode                          |  |  |  |  |

## **2764 vs 6264**

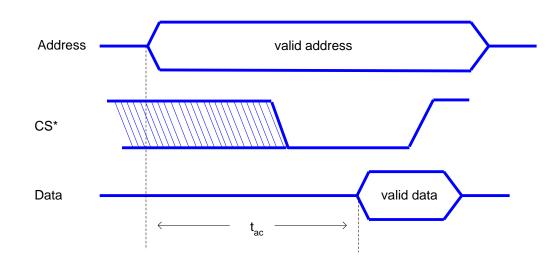

## **Access Time**

- The performance of memory chips normally are based on access time

- Access time (t<sub>ac</sub>) is defined as time taken for the memory to place data onto the data bus as the read signal is received

# **Simple I/O Devices**

## **Input Devices**

- Most input devices do not possess the tristate configuration

- Normally they are connected to other tristate devices such as buffer to ensure proper interface with μP

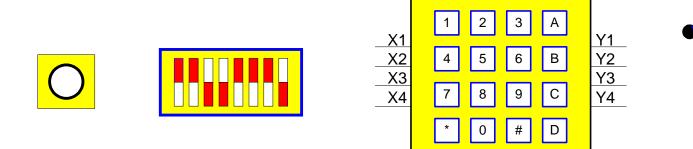

- Common input devices

- Switches (reset, SPST, SPDT etc)

- Keypad

- Sensors

0

0

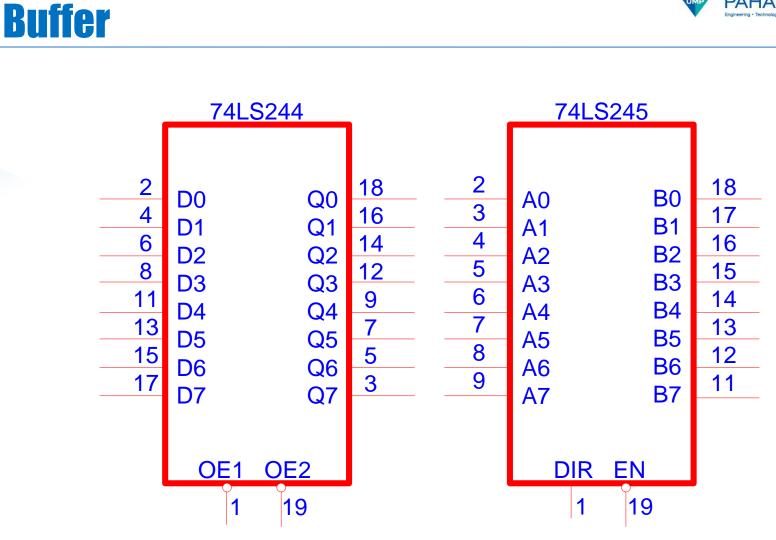

## **Buffer**

Buffer is a circuit that allows any logics onto the data bus

### 74LS244 unidirectional tri-state buffer

- If OE=0, input is allowed to pass through

- If OE=1, output is placed in high impedance

## 74LS245 bidirectional buffer

- A.k.a transceiver

- Data direction is determined by DIR

- If DIR=0, data movement is from A to B

- If DIR=1, data movement is from B to A

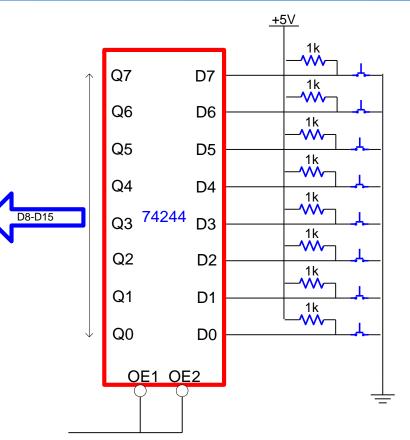

# **Simple Input Interface**

- Simple inputs connection with a buffer

- Enable pins (OE1\* & OE2\*) will activate the buffer and normally are connected to address decoder

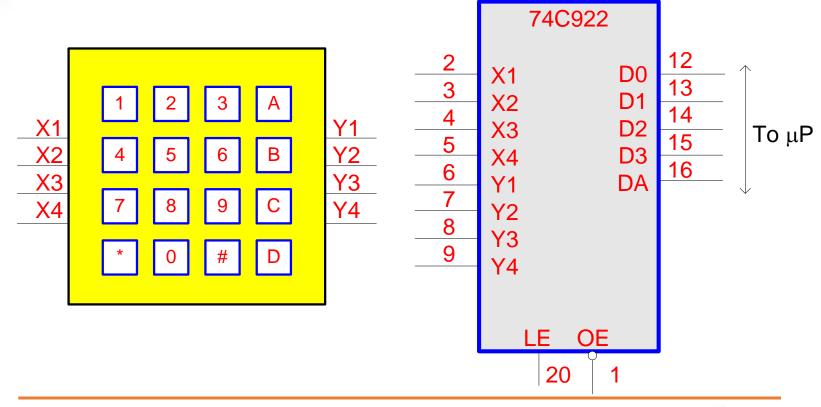

## **Keypad Encoder**

When a keypad is used in a system, a keypad encoder (74922) is required to facilitate the program

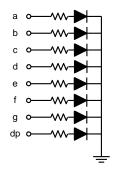

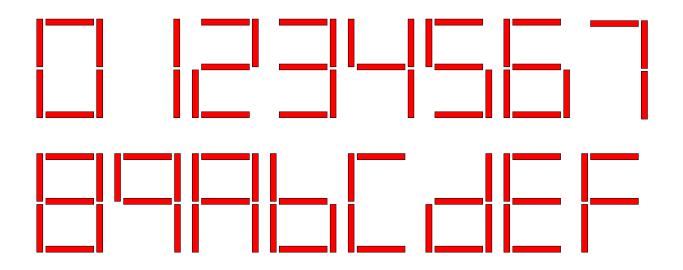

## **Output Devices**

- Like input devices, output devices do not possess the tristate configuration

- They are connected to other tristate devices such as latch for proper interface with processor

- Common output devices

- Light Emitting Diode (LED)

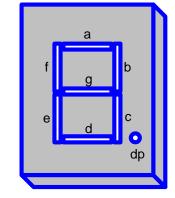

- Seven Segment Display

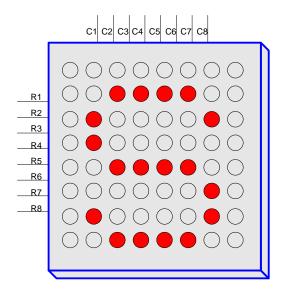

- Dot Matrix

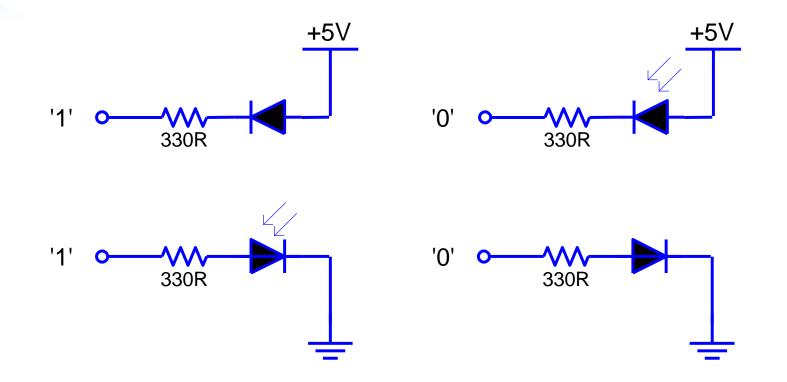

## LED

LED is the most common output device used in microprocessorbased system due its simplicity & cost

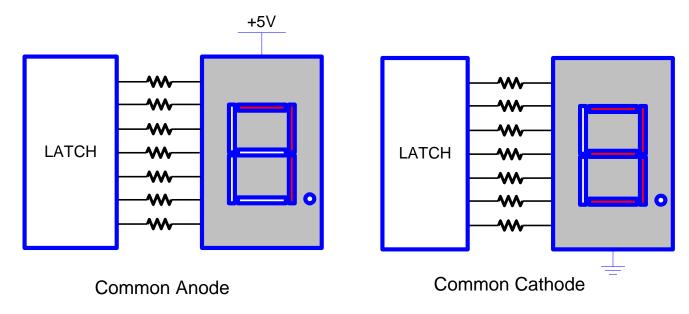

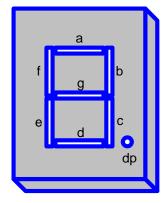

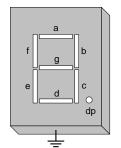

## **7-Segment Display**

There two type configurations

Common Anode

Common Cathode

## **7-Segment Display**

Common CathodeCommon Anode

## **7-Segment Display**

### Common Cathode

|   | а | b | с | d | е | f | g |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4 | 0 | 1 | 1 | 1 | 0 | 0 | 1 |

| 5 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|   | а | b | с | d | е | f | g |

|---|---|---|---|---|---|---|---|

| 8 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| А | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| В | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| С | 1 | 0 | 0 | 1 | 1 | 1 | 0 |

| D | 0 | 1 | 1 | 1 | 1 | 0 | 1 |

| Е | 1 | 0 | 0 | 1 | 1 | 1 | 1 |

| F | 1 | 0 | 0 | 0 | 1 | 1 | 1 |

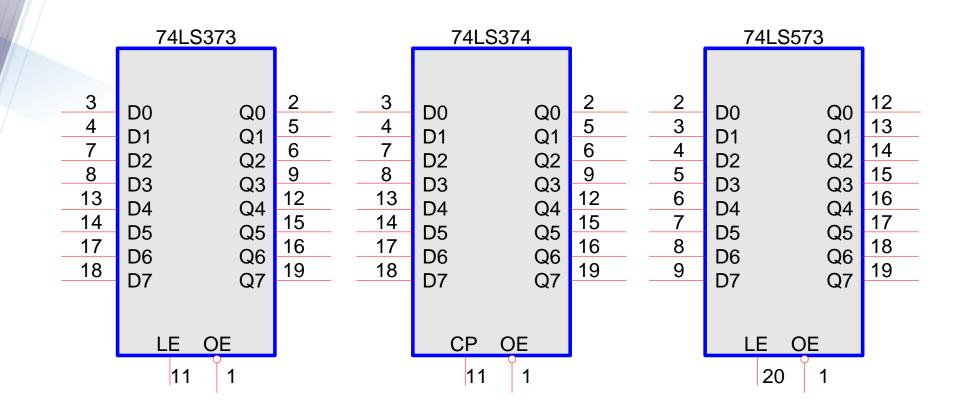

## Latch

Latch is a circuit that capture value at the input

### **74LS373 transparent latch**

- During LE=1, Q=D

- During LE=0, Q hold D during negative edge

- Another version is 74LS573 where the difference is in pin configuration

### ■74LS374 edge triggering

- During positive transition at CP, data is transferred from D to Q

- Another version is 74LS574 where the difference is in pin configuration

Latch

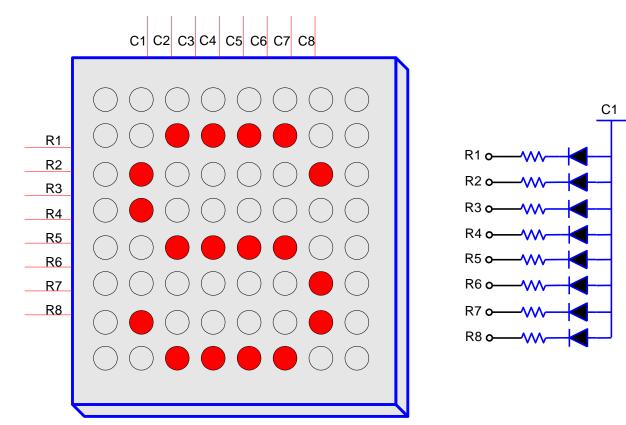

## **Dot Matrix**

A multi-purpose output display, dot matrix is another common output device

## **Self-Test**

Determine the number of address pins and memory capacity of the following EPROM

| Part No    | Capacity (bytes) | Address Pins |

|------------|------------------|--------------|

| TMS27C64   |                  |              |

| HD2716     |                  |              |

| NM27C128   |                  |              |

| 62256LP-10 |                  |              |

| 27C010-15  |                  |              |

| 27C040-15  |                  |              |

| 27512-25   |                  |              |

### Universiti Malaysia PAHANG Ergineergi - Technology - Greativy

## **Self-Test**

### **Exercise**

For ROM chip 27128, find the number of data and address pins. In your opinion what is the minimum pin configuration of the chip

### Exercise

Discuss the number of pins for addresses in (i) 2 kbytes RAM (ii) 512 bytes of RAM

### Exercise

Explain the difference between EEPROM and flash memory

### Exercise

Which memory is used as cache memory in the PC?

### Universiti Malaysia PAHANG Engineering - Technology - Greativy

## **Self-Test**

### Exercise

Explain the role of OE\*, CS\*, WE\* pins in RAM

### Exercise

Why do we need to use latch instead of connecting the output device (such as 7-segment display) directly to the CPU?

### Exercise

What is access time for a memory? Briefly describe the important of fast access time in a microprocessor system by giving an example